SOLVED VEYE IMX327S适配firefly主板问题

-

firefly_linux.config也改了,把摄像头=y了

-

@qianjunzhou

需要分成三部分:- 驱动是否编译到系统中了?

- dts是否正确加载了?

- 硬件i2c是否能检测到了?

我初步比较怀疑的是第二步。 AIO系列使用的dts文件必然与我们做过调试的ROC不是一个上层文件。因此你要首先确认原来系统用的哪个dts文件,然后将camera的定义在相应的文件中引用。

-

@veye_xumm 1.驱动目录下的Kconfig、Makefile已经更改,也生成了veyecam2m.o文件。firefly-linux.config中也添加了相应的驱动开关,然后用firefly的build脚本编译固件

2.我就是在原来的dts中include了veye的dtsi文件,并注释了原本的摄像头dtsi

3.没有驱动信息 -

@qianjunzhou

关于dts的改动,请提供更多信息。

你现在只说你所有步骤都做对了,但是结果不对。我是没办法帮你分析的。 -

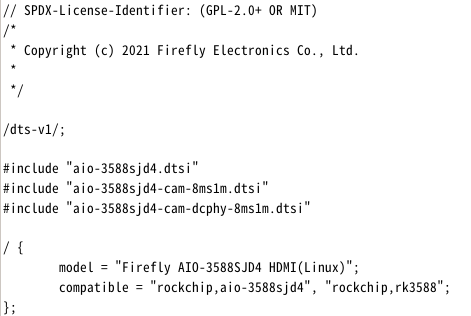

@qianjunzhou 看起来dts应该是在aio-3588sjd4.dts改动一下,包含veyecam的dtsi就可以,逻辑关系还是比较清晰的。

-

这是aio-3588sjd4.dts文件,其中include了两个官方摄像头的dtsi文件,我将aio-3588sjd4-cam-8ms1m.dtsi这个文件的内容替换成了贵司的rk3588-roc-pc-cam-veyecam2m.dtsi的内容

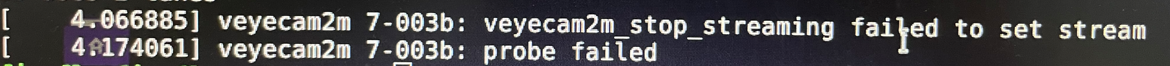

下面是3588sjd4-cam-8ms1m.dtsi这个文件的原内容/* * Copyright (c) 2021 Rockchip Electronics Co., Ltd. * */ / { cam_ircut0: cam_ircut { status = "disabled"; compatible = "rockchip,ircut"; ircut-open-gpios = <&gpio4 RK_PA6 GPIO_ACTIVE_HIGH>; ircut-close-gpios = <&gpio4 RK_PA7 GPIO_ACTIVE_HIGH>; rockchip,camera-module-index = <0>; rockchip,camera-module-facing = "back"; }; vcc_mipidphy0: vcc-mipidcphy0-regulator { status = "disabled"; compatible = "regulator-fixed"; gpio = <&gpio1 RK_PB1 GPIO_ACTIVE_HIGH>; pinctrl-names = "default"; pinctrl-0 = <&mipidphy0_pwr>; regulator-name = "vcc_mipidphy0"; enable-active-high; }; }; &csi2_dphy0 { status = "okay"; ports { #address-cells = <1>; #size-cells = <0>; port@0 { reg = <0>; #address-cells = <1>; #size-cells = <0>; mipidphy0_in_ucam0: endpoint@1 { reg = <1>; remote-endpoint = <&xc7160_out2>; data-lanes = <1 2 3 4>; }; }; port@1 { reg = <1>; #address-cells = <1>; #size-cells = <0>; csidphy0_out: endpoint@0 { reg = <0>; remote-endpoint = <&mipi2_csi2_input>; }; }; }; }; &csi2_dphy0_hw { status = "okay"; }; &i2c5 { status = "okay"; pinctrl-names = "default"; pinctrl-0 = <&i2c5m3_xfer>; XC7160: XC7160b@1b{ compatible = "firefly,xc7160"; reg = <0x1b>; clocks = <&cru CLK_MIPI_CAMARAOUT_M1>; clock-names = "xvclk"; pinctrl-names = "default"; pinctrl-0 = <&mipim1_camera1_clk>; power-domains = <&power RK3588_PD_VI>; power-gpios = <&gpio1 RK_PA7 GPIO_ACTIVE_LOW>; reset-gpios = <&gpio1 RK_PA0 GPIO_ACTIVE_HIGH>; pwdn-gpios = <&gpio1 RK_PA6 GPIO_ACTIVE_HIGH>; //avdd-supply = <&vcc_mipidcphy0>; firefly,clkout-enabled-index = <0>; rockchip,camera-module-index = <0>; rockchip,camera-module-facing = "back"; rockchip,camera-module-name = "NC"; rockchip,camera-module-lens-name = "NC"; port { xc7160_out2: endpoint { remote-endpoint = <&mipidphy0_in_ucam0>; data-lanes = <1 2 3 4>; }; }; }; }; &mipi2_csi2 { status = "okay"; ports { #address-cells = <1>; #size-cells = <0>; port@0 { reg = <0>; #address-cells = <1>; #size-cells = <0>; mipi2_csi2_input: endpoint@1 { reg = <1>; remote-endpoint = <&csidphy0_out>; }; }; port@1 { reg = <1>; #address-cells = <1>; #size-cells = <0>; mipi2_csi2_output: endpoint@0 { reg = <0>; remote-endpoint = <&cif_mipi2_in0>; }; }; }; }; &pinctrl { cam { mipidphy0_pwr: mipidphy0-pwr { rockchip,pins = /* camera power en */ <1 RK_PB1 RK_FUNC_GPIO &pcfg_pull_none>; }; }; }; &rkcif { status = "okay"; // memory-region = <&cif_reserved>; }; &rkcif_mipi_lvds2 { status = "okay"; port { cif_mipi2_in0: endpoint { remote-endpoint = <&mipi2_csi2_output>; }; }; }; &rkcif_mipi_lvds2_sditf { status = "disabled"; port { mipi_lvds2_sditf: endpoint { remote-endpoint = <&isp0_vir0>; }; }; }; &rkcif_mmu { status = "okay"; }; &rkisp0 { status = "disabled"; }; &isp0_mmu { status = "disabled"; }; &rkisp0_vir0 { status = "disabled"; port { #address-cells = <1>; #size-cells = <0>; isp0_vir0: endpoint@0 { reg = <0>; remote-endpoint = <&mipi_lvds2_sditf>; }; }; };开机后,使用dmesg | grep veye会有如下报错

-

@qianjunzhou 好像是I2C不对,这个板子dphy是用I2C5

-

@qianjunzhou

rk3588-roc-pc-cam-veyecam2m.dtsi

中有一些资源信息,需要根据底板不同而调整。比如i2c,io等。 -

@veye_xumm 感谢回复,目前我主板的DPHY上使用贵司的摄像头已经成功了,我的主板只有一个dphy摄像头接口,还剩下两个DCPHY接口但是是24pin的,我想自己画转接板将接口转换一下,但不知道一个主板上能否同时使用两个VEYE的摄像头,是否会有冲突或者别的问题,希望得到您的答复

-

@qianjunzhou 如果主板设计没有问题,那么每一个mipi csi-2接口的硬件资源都是独立的。也就是说,你的3个mipi csi2接口可以接3个摄像头。驱动中需要做的就是dts中区分定义三套资源。

@qianjunzhou said in VEYE IMX327S适配firefly主板问题:

还剩下两个DCPHY接口但是是24pin的

此外,你这个地方提到的DCPHY指的是这两个接口兼容DPHY和CPHY模式对吗? 如果对,则无问题。